Lãnh đạo Samsung dự báo nhu cầu bộ nhớ từ các công ty AI sẽ duy trì ở mức cao đến năm 2027, đồng thời công bố lộ trình sản xuất HBM4.

Tại sự kiện Semicon Korea vừa diễn ra, ông Song Jai-hyuk, Giám đốc công nghệ (CTO) thuộc bộ phận Giải pháp Thiết bị của Samsung, đã chia sẻ những thông tin quan trọng về định hướng phát triển mảng bán dẫn trong tương lai gần.

Theo nhận định của đại diện Samsung, nhu cầu đối với các dòng chip nhớ hiệu năng cao sẽ không chỉ duy trì ở mức đỉnh điểm trong năm nay mà còn tiếp tục kéo dài sang năm 2027. Động lực chính thúc đẩy sự tăng trưởng này đến từ các “AI hyperscalers” – những tập đoàn công nghệ quy mô lớn đang chạy đua xây dựng hạ tầng đám mây khổng lồ để đáp ứng nhu cầu tính toán ngày càng phức tạp của trí tuệ nhân tạo.

Lượng đơn đặt hàng kỷ lục từ nhóm khách hàng này đã và đang đẩy giá thành chip nhớ tăng vọt trên thị trường toàn cầu. Hiện tại, Samsung đang tập trung tối đa nguồn lực cho việc sản xuất hàng loạt thế hệ bộ nhớ băng thông cao tiếp theo là HBM4. Trước đó, báo cáo tài chính quý 3 và quý 4 năm ngoái của hãng đã ghi nhận doanh số bùng nổ nhờ sự thành công của định dạng HBM3E.

Theo lộ trình, Samsung đặt mục tiêu đẩy mạnh kinh doanh dòng HBM4 ngay trong quý đầu tiên của năm nay. Ông Song tiết lộ rằng phản hồi từ các đối tác doanh nghiệp đã nhận được lô hàng HBM4 đầu tiên là “rất khả quan” về mặt hiệu suất hoạt động.

Cải tiến công nghệ liên kết và kiến trúc xếp chồng 3D

Để giải quyết các thách thức vật lý trong việc nâng cao hiệu năng chip nhớ, Samsung đã phát triển thành công công nghệ liên kết lai (hybrid bonding) dành cho HBM. Giải pháp kỹ thuật tiên tiến này giúp giảm 20% điện trở nhiệt đối với các cấu trúc xếp chồng 12 lớp (12H) và 16 lớp (16H).

Các kết quả thử nghiệm nội bộ cho thấy nhiệt độ tại khuôn đế (base die) giảm tới 11%, giúp hệ thống hoạt động ổn định hơn dưới tải nặng. Tuy nhiên, thời điểm thương mại hóa rộng rãi công nghệ liên kết lai này vẫn chưa được công bố cụ thể.

Bên cạnh đó, Samsung cũng giới thiệu công nghệ zHBM, sử dụng phương pháp xếp chồng các khuôn chip theo trục Z. Cách tiếp cận kiến trúc mới này cho phép tăng băng thông bộ nhớ lên gấp 4 lần, đồng thời cắt giảm 25% mức tiêu thụ điện năng so với các giải pháp hiện hành.

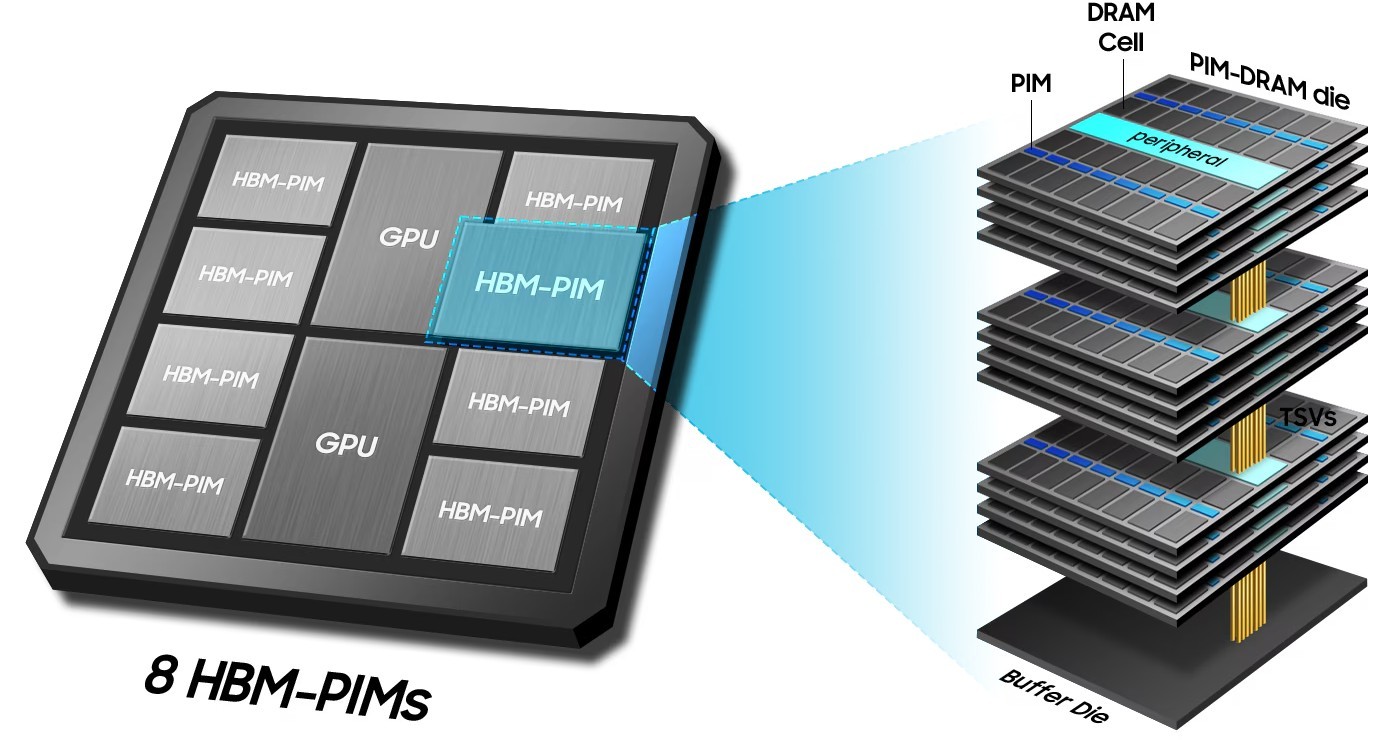

Song song với đó, hãng đang phát triển các thiết kế HBM tùy chỉnh tích hợp khả năng tính toán trực tiếp vào bộ nhớ (Processing-in-Memory hay PIM). Theo CTO Song Jai-hyuk, thiết kế HBM tùy chỉnh này có thể cải thiện hiệu suất xử lý lên 2,8 lần trong khi vẫn giữ nguyên hiệu quả sử dụng năng lượng, mở ra hướng đi mới cho việc tối ưu hóa phần cứng AI.

Nguồn: gsmarena